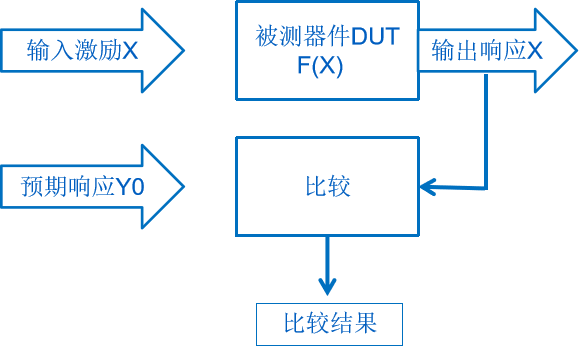

集成电路测试的基本原理

集成电路测试的基本原理是给集成电路信号输入端施加激励,检测其信号输出端的输出响应,并将其与预期的正确响应比较以判别集成电路功能的功能和性能的好坏

集成电路测试的意义与作用

集成电路测试的意义:

随着集成电路应用领域扩大,其大量用于各种整机系统中。在系统中集成电路往往作为关键器件使用,其质量和性能的好坏直接影响到了系统的稳定性和可靠性。在系统级的性能测试分析和故障诊断时,集成电路测试的可行性和便利性会带来决定性影响。

集成电路测试的作用:

集成电路测试时确保产品良率和成本控制的重要环节,在集成电路生产过程中起着举足轻重的作用。集成电路测试的主要目的时保证芯片在恶劣环境下能完全实现设计规格书所规定的功能及性能指标。每一道测试都会产生一系列的测试数据,由于测试程序通常是有一系列测试项目组成的,从各个方面对芯片进行充分检测,不仅可以判断芯片性能是否符合标准,是否可以进入市场,而且能够从测试结果的详细数据中充分、定量地反映出每颗芯片从结构、功能到电气特性的各种指标。因此,对集成电路进行测试可有效提高芯片的成品率以及成产效率。

集成电路测试过程

集成电路测试环节包括:

1.可测性评估、测试方案制订

2.器件接口板设计

3.测试程序开发

4.测试数据分析与资料归档

常规数字集成电路参数测试

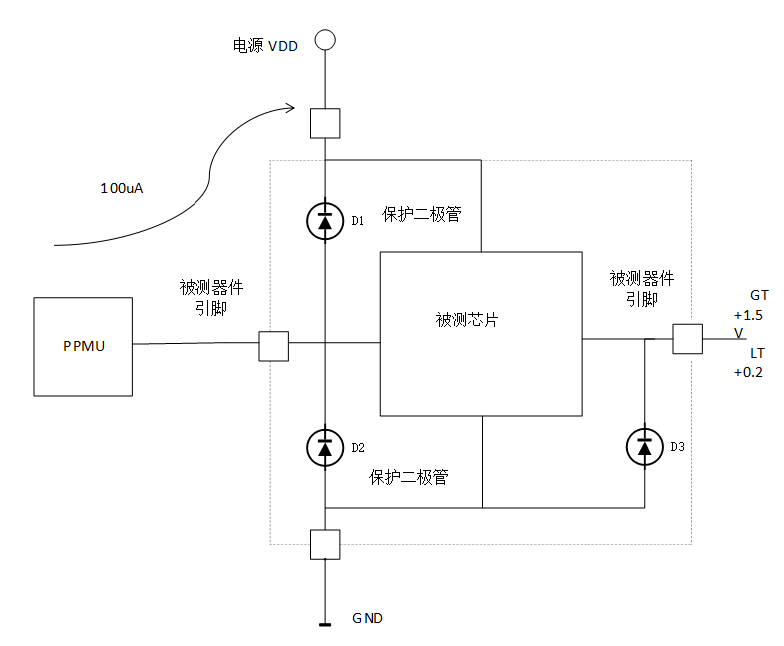

- 连接性测试(CON):

目的:连接性测试旨在验证被测器件管脚的电气连接是否正常,确保输入钳位二极管在正常工作条件下能够正常运作。当输入输出管脚接收到的电流超过电压限制值时,二极管应能将电流导入地或电源,从而保护电路。以及保证管脚与管脚之间、管脚与地、电源之间不存在开路或短路情况。这对于区分芯片缺陷和测试硬件连接缺陷至关重要。

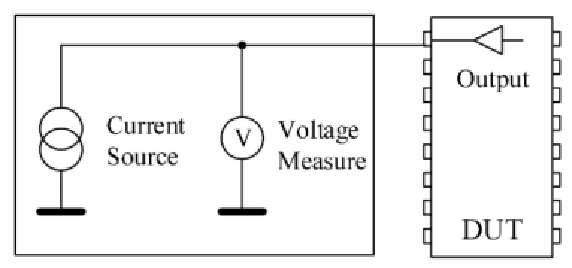

测试方法:测试时向DUT被测引脚内部二极管注入一个正偏电流(灌电流)通常为100uA,并且VDD=0,此时如果器件连接正常,二极管正向导通电压对与硅管来说大约在0.55V到0.75V范围内

连接性测试原理图:

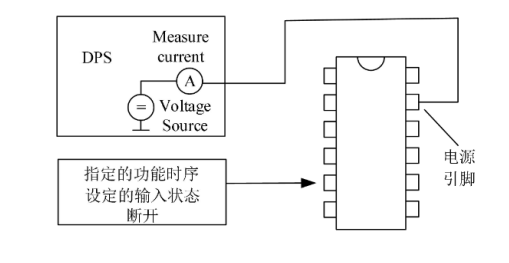

- 电源电流测试(IDD/VCC):

检测器件严重缺陷的最快方法之一是测量其吸收的电源电流的大小,集成电路出现的严重缺陷包括金属短路的,光掩膜错误,蚀刻未完成,表面杂质等,会造成电源到地的短路等灾难性故障。同时确保被测芯片的稳定性和可靠性

测试时使用DPS电源板卡向电源管脚施加直流电压并且测量管脚电流,判断是否在规定范围内。

原理图:

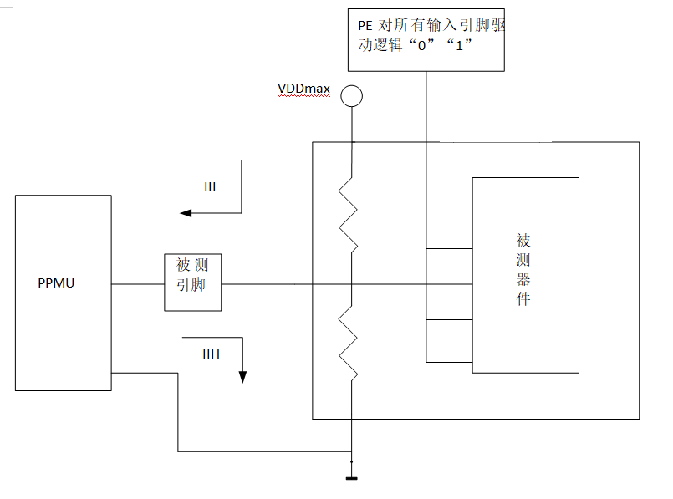

- 漏电流测试(II):

芯片内部晶体管不可能在理想的状态,因此或多或少会存在一定的漏电流,需要测试漏电,保证漏电是在正常的允许的范围内,而不是潜在的缺陷。

在被测芯片的输入引脚或输出引脚施加直流电源,若在该引脚上检测到微弱的电流变化则证明被测芯片漏电,漏电流一般要测两次,先在管脚电压接近正电源电压处检测,然后在接近地(或负电压)处检测一次,分别称为IIH(输入电流,高逻辑)、IIL(输入电流,低逻辑)。对数字管脚则是在输入阈值电压VIH和VIL下分两次测试。模拟输入管脚则按数据表中的特定电压电平测试。如果未指定输入电压,则应检测在所有允许输入的电压范围侧漏电流的最大值。

漏电流测试原理图:

- 功能测试(FUN):

功能测试用于测试器件是否能够完成设计所预期的所有工作或功能。逻辑I/O通过一定方法在器件中传输,确保对器件的每一个内部节点都进行了工作正常与否的验证。功能验证有时也称为时钟速率、节点或真值表测试。静态功能测试常用真值表测试的方法。

测试时编写 Pattern 码型文件;设置输入高/低电平和输出高/低电平的值(VIH 一般与 VCC 的值一样,VIL 一般设置为 0);编译 Pattern 码型文件;输入 Pattern 码型文件,若输出电平满足条件,则通过测试,反之,显示错误原因。

- 输入高低电平测试(VIHL):

VIH指输入高电压,VIL指输入低电压,在所选芯片的数据手册中常会对VIHL指定一个范围,包括最大值,典型值和最小值。

进行测试时,虽然无法直接测量输入电平,但可以通过功能测试来判断输入电平是否符合设计范围。

- 输出高低电平测试(VOHL):

此项目的目的是测试高低电平判决,验证芯片在不同输入电平下的功能和性能表现以确保芯片的逻辑功能输出正常。测试有助于工程师发现可能存在的设计缺陷、制造问题或环境适应性不足等问题。

原理图:

- 传输延迟测试(Tdelay):

传输延迟是指输入端产生一个状态(边沿)转换和导致相应的输出端的状态(边沿)转换之间的延迟时间。这个时间从输入端的某一特定电压开始到输出端的某一特定电压结束。它是反映数字集成电路对信号响应速度的一个重要指标。对于高速芯片来说,延迟尤为重要。传输延迟测试时,一般时通过测试系统给DUT的驱动端发送测试信号,经由被测信号数字通道的传输路径后到达测试系统DIB的通道末端。在此过程中测试DUT输入信号发出和接收到输出信号的时间间隔,即为DUT的传输延迟时间。

- 传输延迟上升/下降时间测试(TPHL/TPLH):

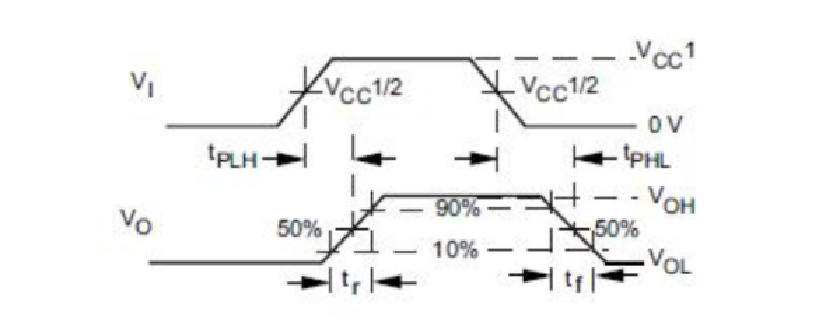

TPHL/TPLH指输入端在施加规定的电平和脉冲电压时,输出脉冲电压由高电平到低电平/低电平到高电平的边沿和对应的输入脉冲电压边沿上两规定的参考电平间的时间。

测试时被测输入端施加脉冲电压,其余输入端施加规定电平;被测输出端接负载,其余输出端开路。在被测输出端输出脉冲电压由高到底/低到高电平边沿的参考电平VREF处和对应的输入脉冲电压边沿的参考电平VREF的两者之间测得的时间间隔即为输出由高到底/低到高电平传输延时时间.

传输延迟上升/下降时间测试(TPHL/TPLH)原理图:

Comments 1 条评论